Verilog書いてて失敗した事のメモ VerilogLog,略してVeriLog

set RTL_FILE "[glob rtl/*.v]"

regsub {rtl/ctrl_b12n8_1.v} $RTL_FILE {} RTL_FILE

regsub {rtl/ctrl_b12n8_2.v} $RTL_FILE {} RTL_FILE

:set行の下に,regsubで削除したいファイル行を続ける.

TiminigInfo..やAreaInfo..をまとめるのめどい

cp /home/tsukamoto/vhd/rep2csv.rb /home/じぶんち/vhd/プロジェクト名

で,

ruby ./rep2csv.rb

とするとrepディレクトリ以下のレポートファイルをてきとうにパーズして csv形式で面積と遅延時間を出力します.csv形式なんでOooとかexcelでどうぞ. ご意見あればどうぞ.

別のalways文で同じ信号をドライブしないこと. 当たり前だけど,multiple driver うんぬん言われて シミュレーションできても合成できなくなるぞう

readで回路記述を読み込んだ後

source scr/typ_lib_starc90nm.scr

する.

つぎに

set_max_delay 5 -to [all_outputs] set_max_area 5

などとして時間,面積制約を加えた後

Design -> Compile Ultra

このとき,"No auto ungroup"にチェックしたほうが速い場合がある. (独自設計の場合など)

Select -> Path from/through/to

で,何も入力せずに[OK]とすると最長経路を選択できる(delay type が max?).

さらに

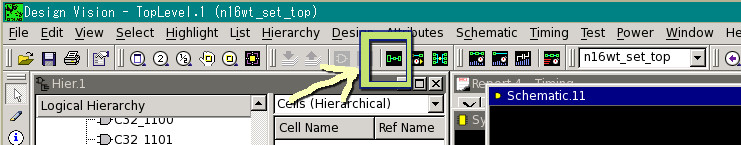

Create PathSchematic of Selection (3つ並びのアイコンの右側)

で,その経路図を抽出できる.

遅延時間は

Timing -> Report Timing Path